# Quantum Architecture: From Devices to Systems

Workshop on Quantum Information Science – Vienna, VA April 24, 2009

Isaac Chuang

MIT EECS & Department of Physics

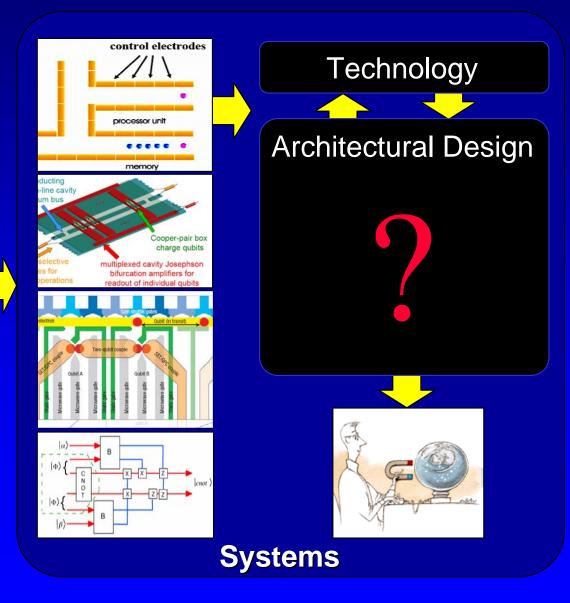

### The Q. Architecture Challenge

### **DiVIncenzo**

- 1.Qubits

- 2.Universal gates

- 3.Input state

- 4.Measurement

**Theory**

Lessons learned...?

### Architecture: Lessons

Devices + Architecture = System which is...

- 1. Reliable

- 2. Parallelizable

- 3. Programmable

- 4. Debuggable

- 5. Predictable

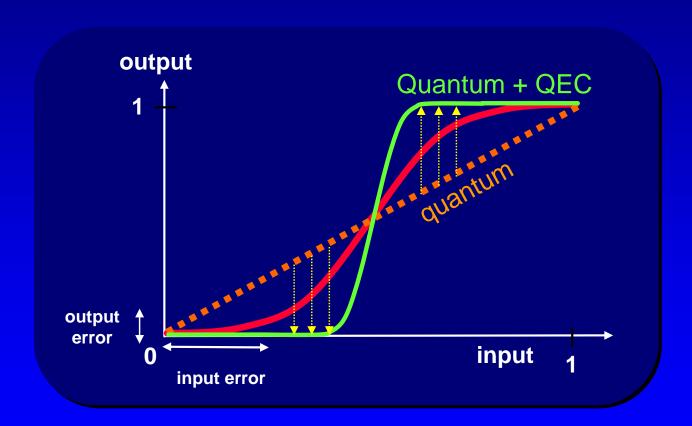

## **Device Scalability**

Why are vacuum tubes (or CMOS) scalable?

- Quantum gates are intrinsically unstable!

- Need a different approach: Error Correction

### Fault Tolerance Theorem

Reliable computers can be constructed from faulty components

• A circuit containing N (error-free) gates can be simulated with probability of error at most  $\epsilon$ , using N log(N/ $\epsilon$ ) faulty gates, which fail with probability p, so long as p<p<sub>th</sub>. von Neumann++ (1956)

Quantum version: Shor, Preskill, Aharonov, Ben-Or, Knill, Laflamme, Zurek, ...

### Fault Tolerance & QC

In a FT QC, >99% of resources spent will probably go to quantum error correction!

The requirements for fault-tolerance determine how a quantum computer may be physically realized

• Max device err  $p_{th}$  = (# ways to get > 1 error)<sup>-1</sup>

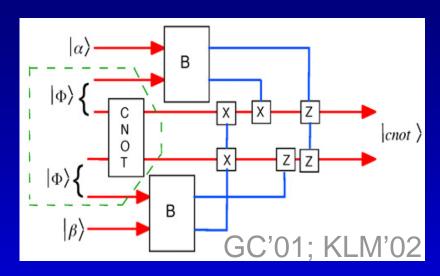

### Case Study: Linear Optics

- Capability:

- Reliable single qubit ops

- CNOT with  $p_{fail}$  ~ 89%

- Recipe:

Ralph, Rep. Prog. Phys. **69** (2006)

- Repeat ancilla states creation until successful

- Rely on good photon-number measurements

- $p_{th} < 3 \times 10^{-3}$  photon loss,  $10^{-4}$  depolarization

- Need ~10<sup>20</sup> bell pairs per operation!

Dawson, Haselgrove, Nielsen, PRL 96, 020501 (2006); quantph 0601066

### Architecture: Lessons

Devices + Architecture = System which is...

1. Reliable

- > 99% of QC = Error Correction

- 2. Parallelizable

- 3. Programmable

- 4. Debuggable

- 5. Predictable

### Q Factoring: Space vs Time

- Problem: Factor N bit number

- Shor's algorithm needs

| ~N              | ~2N <sup>2</sup>        | ~N <sup>3</sup>     | qubits |

|-----------------|-------------------------|---------------------|--------|

| ~N <sup>3</sup> | ~9N(log <sup>2</sup> N) | ~log <sup>3</sup> N | steps  |

• Ex:  $N=663 \Rightarrow 10^6$  qubits, ~ $10^6$  ops 150 hours (1Hz QC) ...6 days!

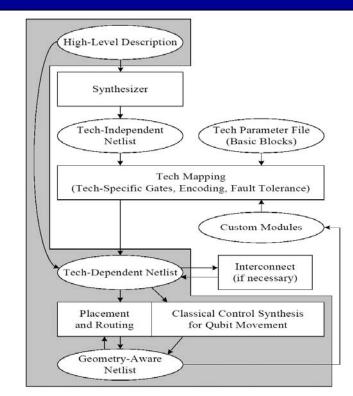

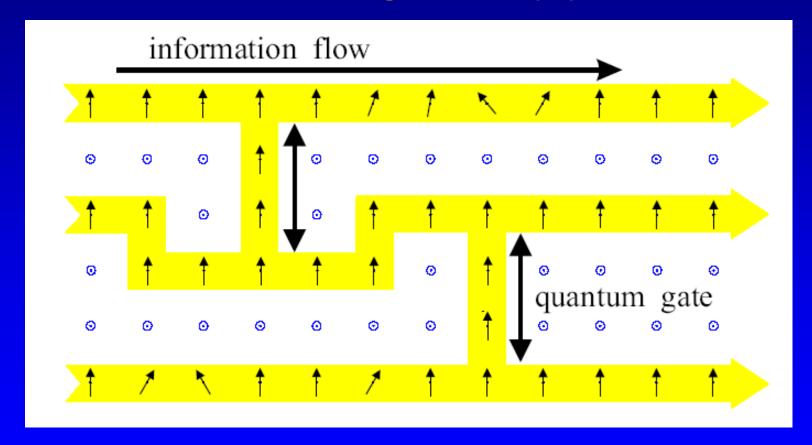

### Scheduling Q. Resources

Problem: qubit movement & gates

### Results:

- QUALE (U. Wash.): map q. circuit onto physical layout, using Path-Finder (ions)

- QPOS (U. Davis): schedule physical ops; classical instr. scheduling heuristics (dots)

- QPU toolchain (Princeton): stagger ops to optimize fault tolerance (e<sup>-</sup> on LHe)

- Quantum CAD (Berkeley): dataflowanalysis; greedy congestion relief (ions)

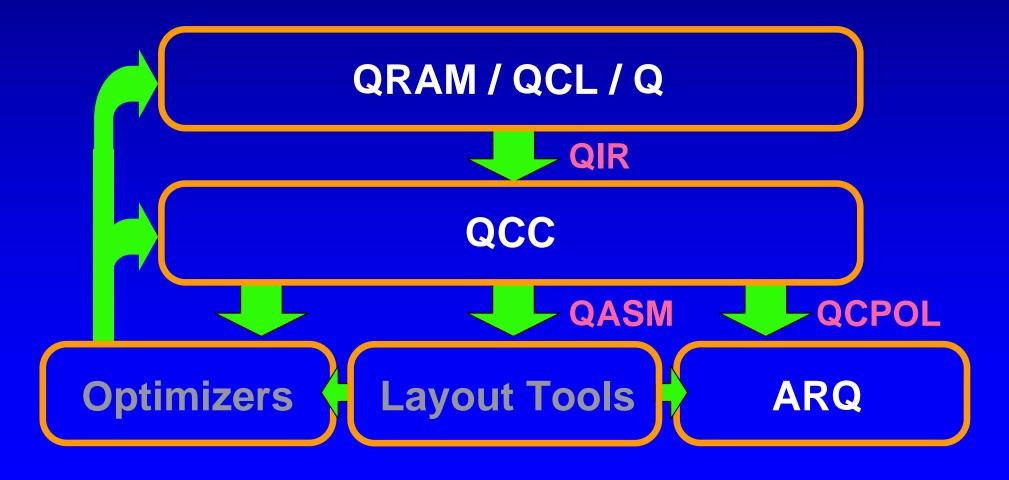

Figure 4: An overview of our CAD flow for quantum circuits. Ovals represent files; rectangles represent tools.

### Architecture: Lessons

Devices + Architecture = System which is...

- 1. Reliable > 99% of QC = Error Correction

- 2. Parallelizable Depth / Time / Movement Tradeoff

- 3. Programmable

- 4. Debuggable

- 5. Predictable

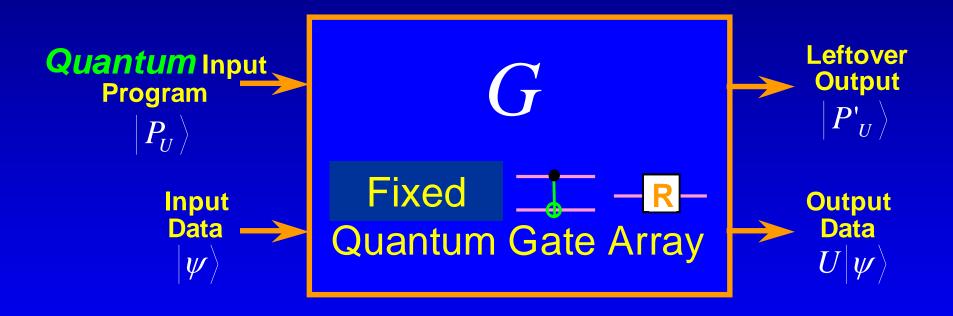

### **Quantum Circuit Model**

CNOT + single qubit gates, |0>,

### Quantum controlled QC

Model: teleport gates...

Catch – only certain programs efficiently implementable

### Quantum Software

- Universal, Fault Tolerant QC:

- Single qubit operations

- Bell basis measurements

- A supply of entangled states

D. Gottesman, I. Chuang, Nature, v402, p390, 1999

### Quantum: uncopyable & single-use!

- Inherently hold value marketable commodities

- Significantly simplify hardware requirements

- Can be checked at the factory

- Delivered via a "quantum internet"

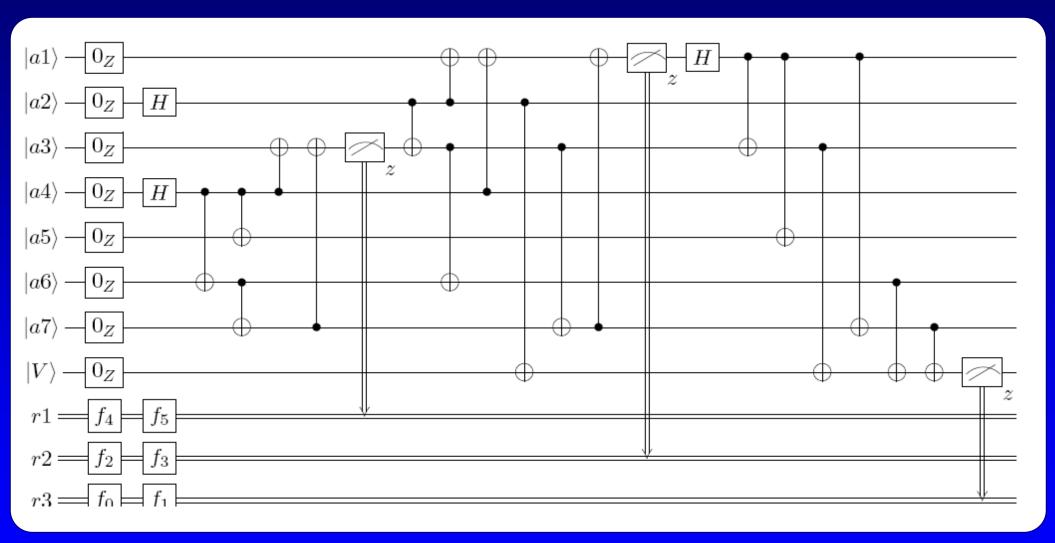

### Measurement-based QC

R. Raussendorf and H. J. Briegel. PRL 86(22):5188-5191, 2001

Recipe: Create state, then measure

"measurement" based models of QC

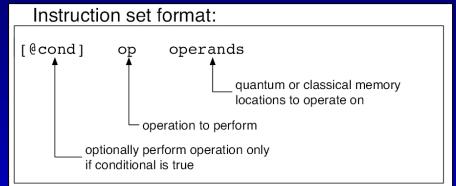

### Q. Programming Languages

### Highly active field!

- •QRAM (Knill'96): register machine

- •QCL (Omer'98-'03): C-like

- **Quantum** λ-calculus (Maymin'96,...)

- •QML (Altenkrich & Grattage'05): q. control & data

- Meas. QC (Danos et al'04,...): patterns

- •QPAIg (Jorrand'04-...): formal verification

- •Q-HSK, SQRAM, Q-gol, qGCL...

- 100 papers (1996-2007)

- Open issue: fault tolerance?

#### **Quantum Operations:**

| h       | dN         | Basic quantum primitives such as Hadamard (H), invert (X), invert phase (Z), arbitrary rotation (R), and phase gate (S) |  |

|---------|------------|-------------------------------------------------------------------------------------------------------------------------|--|

| х       | dΝ         |                                                                                                                         |  |

| z       | qN         |                                                                                                                         |  |

| rot     | qN,real    |                                                                                                                         |  |

| s       | dΝ         |                                                                                                                         |  |

| v       | qN,qC,real | rotate qN about X axis, conditional on qC, by real                                                                      |  |

| cnot    | qN,qC      | flip qN conditional on qC                                                                                               |  |

| swap    | qN1,qN2    | swap qN1 and qN2                                                                                                        |  |

| toffoli | qN,qC1,qC2 | flip qN conditional on qC1, qC2                                                                                         |  |

| measure | cT, qN     | measure qN place result in cT                                                                                           |  |

QUALE (U. Washington)

### Architecture: Lessons

Devices + Architecture = System which is...

- 1. Reliable > 99% of QC = Error Correction

- 2. Parallelizable Depth / Time / Movement Tradeoff

- 3. Programmable Many new models ; FT lang?

- 4. Debuggable

- 5. Predictable

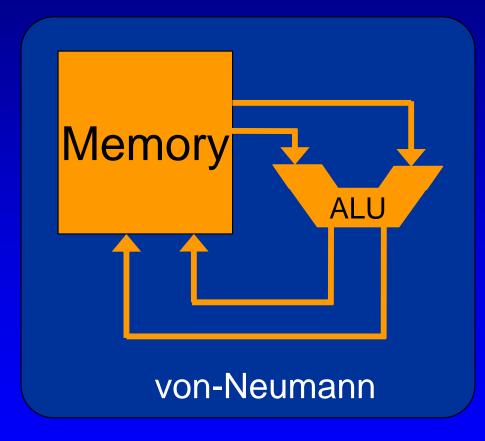

### **Architecture Concepts**

1940's: von Neumann – Programmable Systems

- Stored program; modular design

- Blocks simplify debugging!

### **Architecture Concepts**

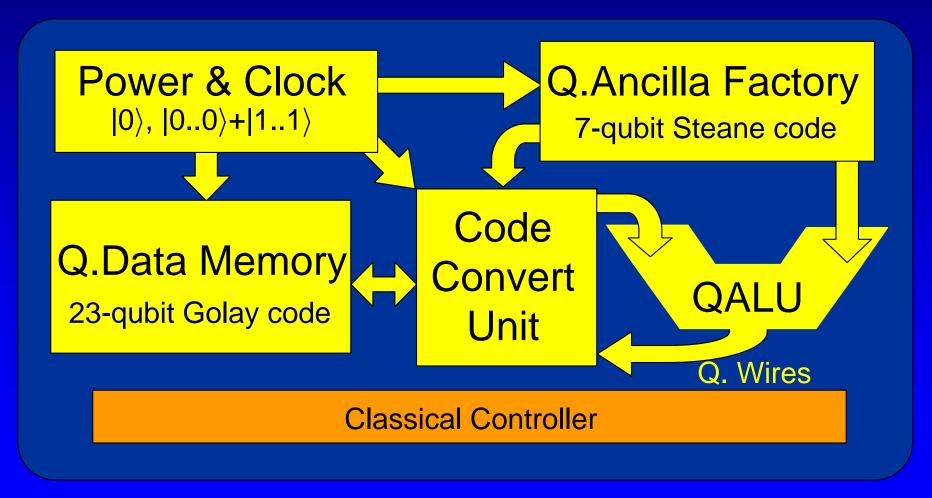

Modern Q. computer arch. = seek reliability

Knill; Nielsen & Chuang; Steane; Chong, Chuang, Kubiatowicz, Oskin – IEEE Computer 2006

### Architecture: Lessons

Devices + Architecture = System which is...

- 1. Reliable > 99% of QC = Error Correction

- 2. Parallelizable Depth / Time / Movement Tradeoff

- 3. Programmable Many new models ; FT lang?

- 4. Debuggable Wires = teleport; power = entanglement

- 5. Predictable

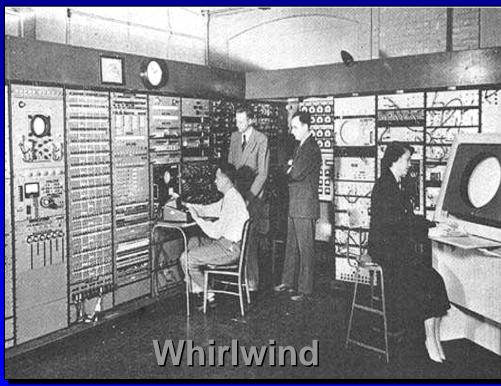

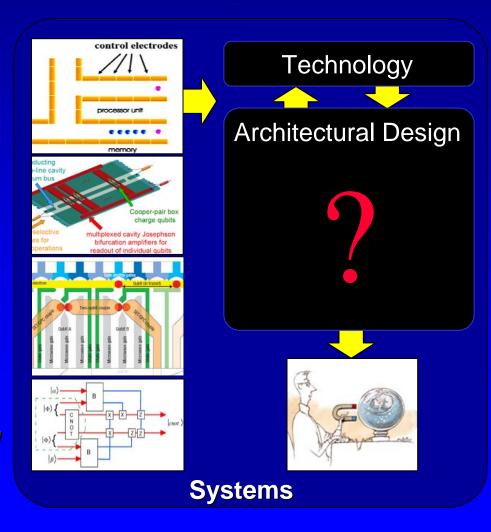

## Real large-scale computing systems are designed & verified far in advance of implementation, with predictive tools

Whirlwind  $\rightarrow$  SPICE  $\rightarrow$  ... Behavioral synthesis  $\rightarrow$  Formal verification  $\rightarrow$  Physical verification

### Large Scale, Reliable QC

- System: 10<sup>6</sup> qubits, >10<sup>6</sup> logical gates

- FTQC ~10<sup>7</sup> to 10<sup>8</sup> qubits & physical gates (7-qubit Steane code, 1-2 concat. levels)

- Questions:

- How many lasers required? Laser power?

- How large an ion trap chip?

- What kind & size of classical control?

- What fault tolerance threshold?

(gate / state / memory / movement)

Approach: Simulate QECC (efficient!)

## Quantum Design Tools

·Vision: Layered hierarchy with simple interfaces

### Predictive QC Design Tool

Predict performance before building!!

### **INPUT**

- -Technology

- Gate performance

- Comm. constraints

- Control capability

- Memory fidelities

- Geometric constraints

- Q. Code

- Entanglement supply

FT Eng.

Design

Analysis

simulate basic

**IEEE Computer, 2002 & 2006**

QEC blocks & I/O

### **OUTPUT**

- p<sub>th</sub> for gates, wires,

memory, state supply

- Logical gate speed

- Space, time required

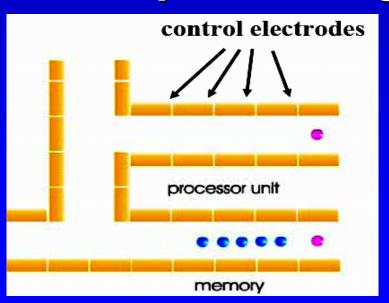

## Trapped Ion FTQC

- Wealth of expt. data

- Teleportation (3 ions)

- Superdense coding (2 ions)

- QFT; Q. error correction (3 ions)

- GHZ and W states (4-8 ions)

- Conceptual design

| Timescales                    |                  |  |  |  |

|-------------------------------|------------------|--|--|--|

| Single Qubit Gate             | 1 μs             |  |  |  |

| Two Qubit Gate                | 10 μs            |  |  |  |

| Measure                       | 100 μs           |  |  |  |

| Cool a linear chain           | 10 ms            |  |  |  |

| Movement                      | 10 ns / μm       |  |  |  |

| Split a linear chain          | 1 ms             |  |  |  |

| Join two linear chains        | 0 seconds        |  |  |  |

| Memory time (not implemented) | 100 seconds      |  |  |  |

| Failure Probabilities         |                  |  |  |  |

| Single Qubit Gate Failure     | 0.0001           |  |  |  |

| Two Qubit Gate Failure        | 0.03             |  |  |  |

| Measurement Failure           | 0.01             |  |  |  |

| Movement Failure              | 0.005 / μm       |  |  |  |

| Heating <n></n>               |                  |  |  |  |

| Moving a Linear Chain         | 0.01 quanta / μm |  |  |  |

| Splitting a Linear Chain      | 1 quanta         |  |  |  |

| Cpmmig a Emeai oriani         | 7 quente         |  |  |  |

If

$$p_{err}^{meas} \sim 10^{-4}$$

$p_{th} \sim 4 \times 10^{-4}$

**Cross (2006)**

Kielpinski, Monroe, and Wineland, "Architecture for a Large-Scale Ion-Trap Quantum Computer," Nature 417, 709 (2002)

## Trapped ion Factoring?

Case Study: Quantum Logic Array

Trapped ions ; fault tolerant ; NIST parameters

# **Quantum** Computing for Computer Architects

Tzvetan Metodi Frederic T. Chong **TABLE 9.2:** System Numbers for Shor's Algorithm for Factoring an *N*-bit Number Using the Circuit Descriptions of [154, 155] and the QLA Microarchitecture Model. The QLA Chip Area is Determined by the Number of Logical Qubits and Channels.

|                | N = 128 | N = 512   | N = 1024  | N=2048     |

|----------------|---------|-----------|-----------|------------|

| Logical qubits | 37,971  | 150,771   | 301,251   | 602,259    |

| Toffoli gates  | 63,729  | 397,910   | 964,919   | 2,301,767  |

| Total gates    | 115,033 | 1,016,295 | 3,270,582 | 11,148,214 |

| Area $(m^2)$   | 0.11    | 0.45      | 0.90      | 1.80       |

| Time (days)    | 0.9     | 5.5       | 13.4      | 32.1       |

SYNTHESIS LECTURES ON COMPUTER ARCHITECTURE

Mark D. Hill, Series Editor

Metodi et al, ISCA 2006

## **Summary**

We are on the verge of being able to build largescale quantum information processing systems!

- Architecture is key\*

- Challenges:

- Build predictive tools to DESIGN & VERIFY

- Feedback to strategically improve QC technology

- Contribute back to classical computation (fault tolerance, low power)

<sup>\*</sup> Science – not just for mission agencies